AMBA AXI Infrastructure Based on Xilinx FPGA IPs and Verilog

Why take this course?

🌟 Mastering AMBA AXI Infrastructure with Xilinx FPGA IPs and Verilog 🌟

Why AXI? 🤔

AMBA AXI protocol is the cornerstone of modern System on Chips (SoCs). It's integral to any processor or complex system, including those crafted by heavyweights like Xilinx, Intel, and AMD. With the burgeoning field of AI, AXI protocol's importance is only set to increase as it becomes a staple in high-performance computing applications.

Target Students 🎓

This course is designed for:

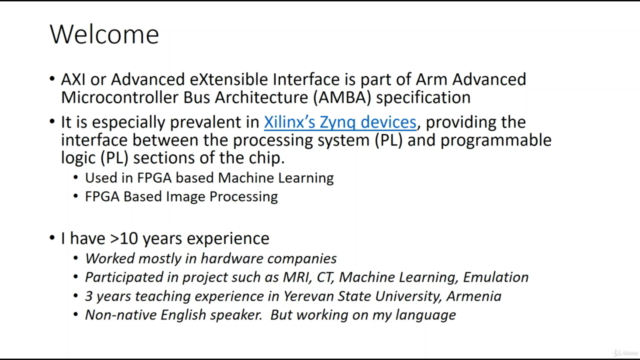

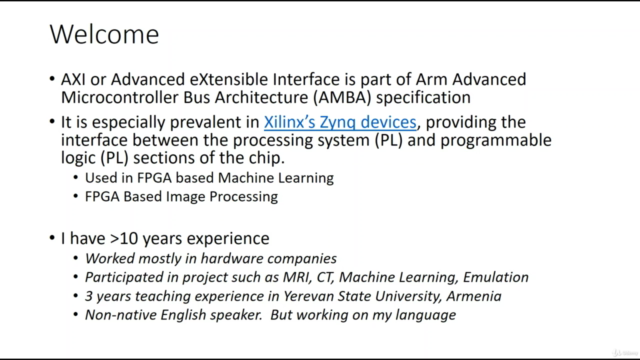

- FPGA Designers: Who are already incorporating AXI based modules into their designs, and want to deepen their understanding.

- Engineers new to AXI protocol: Seeking to grasp the basics of AXI communication.

- Graduate Students: Looking for employment opportunities in FPGA or SoC development, as knowledge of AXI has been a common litmus test in my previous three companies.

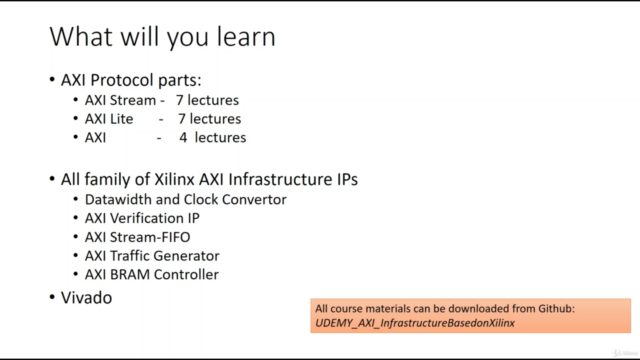

Course Content 📚

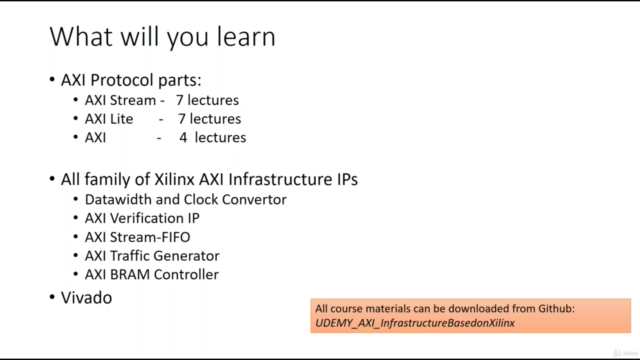

This course offers a comprehensive dive into the AXI protocol family, with a practical approach to using AXI-based IPs from Xilinx. We'll cover:

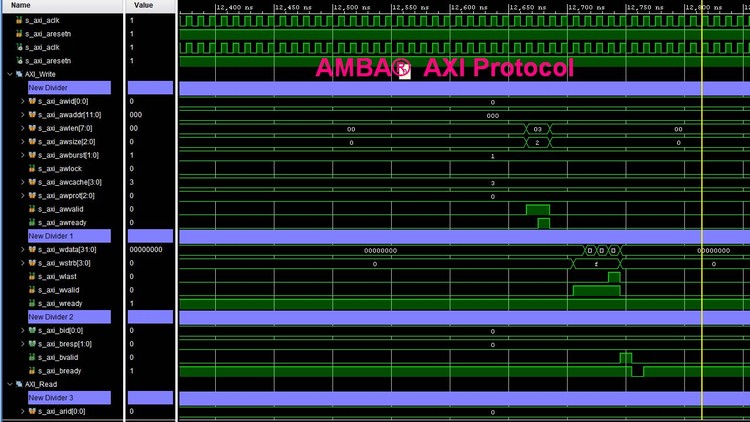

- AXI Stream: The easier introduction to understanding AXI.

- AXI Lite: An in-depth exploration of this fundamental sub-protocol.

- Verilog Designs: Practical implementations using Verilog, the language of choice for hardware description.

- Simulation Methods: Gain proficiency in simulating AXI protocol interactions.

- ARM Specification Review: Learn to interpret ARM's technical specifications, a crucial skill for any AXI practitioner.

Special Thanks 🙏

A heartfelt thanks to Eduard Vardanyan from ARM, whose expertise and guidance were indispensable in creating this course. His contributions have been instrumental in simplifying complex aspects of the AXI protocol.

Caution ⚠️

Please note that while I strive for clarity and accuracy, my non-native English might occasionally lead to grammatical errors or misunderstandings. I assure you that these minor imperfections will not hinder your learning experience as we focus on the substance of the material rather than its presentation.

Course Materials 🛠️

All course materials, including code samples, can be found and downloaded from our dedicated GitHub repository.

Note to Software Background Learners: A foundational understanding of Verilog is recommended for certain lectures that delve into hardware implementation details. If you're not already familiar with Verilog, consider brushing up on the basics before diving into this course.

Join us and unlock the secrets of AMBA AXI Infrastructure with Xilinx FPGA IPs and Verilog! 🎬🎉

Don't miss out on the opportunity to master one of the most critical components in modern SoC design. Enroll now and take a significant step towards becoming an expert in ARM-based systems, FPGA development, and high-speed communication protocols. Let's embark on this learning journey together! 🚀✨

Course Gallery

Loading charts...