Step by step hands-on design of UART using Verilog HDL

Why take this course?

🌟 Course Title: Step by Step Hands-On Design of UART using Verilog HDL 🚀

Course Headline: Master UART Modules and Their Implementation with Verilog HDL 🧪✨

Course Description:

Are you ready to dive deep into the world of serial communication and master the Universal Asynchronous Receiver/Transmitter (UART) protocol through the lens of Verilog Hardware Description Language (HDL)? This comprehensive course is tailored for both novices and experienced engineers looking to solidify their understanding of UART modules and their implementation in Verilog HDL.

Why Study UART with Verilog HDL?

- Fundamentals of UART: We'll begin by laying the groundwork for understanding what UART is, why it's essential, and its advantages over traditional parallel communication.

- UART Protocol Unpacked: Gain a crystal-clear grasp of how UART operates, including the internal modules that make it function and the transfer operations that facilitate data transmission and reception.

- Design with Precision: Learn to design UART internal modules like Transmitter and Receiver using Finite State Machines (FSMs) and understand the intricacies of the Baud Rate Generator's role in timing and synchronization.

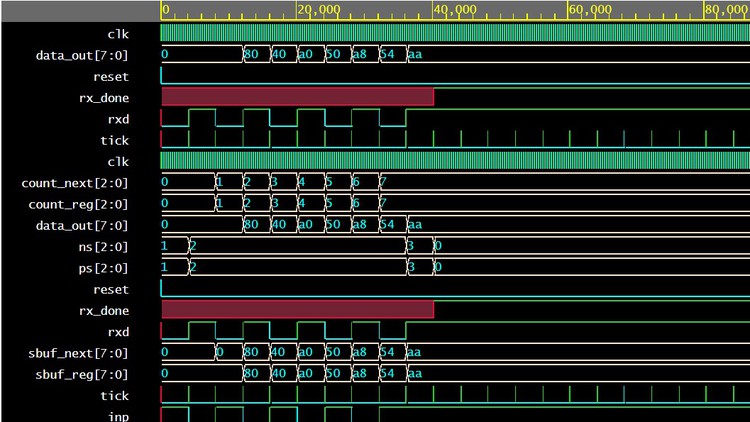

- Testing Your Design: Discover how to set up a test bench environment for your designs, select relevant test points, and integrate them with your design for effective testing and debugging.

- Real-World Application: Get hands-on experience writing Verilog HDL code for UART modules, including Transmitter, Receiver, and Baud Rate Generator, and understand the importance of state machine variables in the process.

Course Highlights:

- Detailed Tutorials: Step-by-step guidance on each aspect of UART design, from the basics to advanced topics.

- Practical Exercises: Hands-on tasks designed to reinforce your learning and help you apply what you've learned in real-world scenarios.

- State Machine Mastery: Learn how to implement FSMs for UART using Verilog, which is crucial for understanding the timing and control logic within the UART module.

- Test Bench Creation: Gain proficiency in creating a test bench environment that simulates real-world conditions and helps you validate your designs.

- Debugging Techniques: Learn effective methods for debugging your Verilog HDL code and analyzing output waveforms to ensure your design functions correctly.

What You Will Learn:

- The importance of serial communication over parallel communication.

- How UART facilitates asynchronous data transfer between devices.

- The internal workings of a UART module, including its data format and operation modes.

- Writing Verilog HDL code for UART modules, including both the Transmitter and Receiver components.

- Designing a Baud Rate Generator using Verilog HDL for precise timing control.

- Creating and utilizing a test bench environment to simulate and validate your UART design.

- Troubleshooting and debugging techniques to ensure your UART system operates flawlessly.

Who Should Take This Course? This course is ideal for:

- Engineers looking to expand their knowledge of UART protocols in the context of Verilog HDL.

- Designers aiming to implement UART communication in embedded systems and FPGAs.

- Students aspiring to enter the field of digital design with a solid foundation in UART and Verilog HDL.

Join us on this journey to become an expert in UART design with Verilog HDL, and transform your career with this essential skill set! 🛠️🔬🚀

Enrollment is open! Secure your spot now and embark on a learning adventure that will set you apart in the field of digital design. 🎓👍

Loading charts...