VSD - Static Timing Analysis - II

Why take this course?

🌟 Course Title: VSD - Static Timing Analysis - II

📚 Course Description:

Unlock the Secrets of Chip Timing with Opentimer 🚀

Course Headline: VLSI - Analyse your chip timing for free!

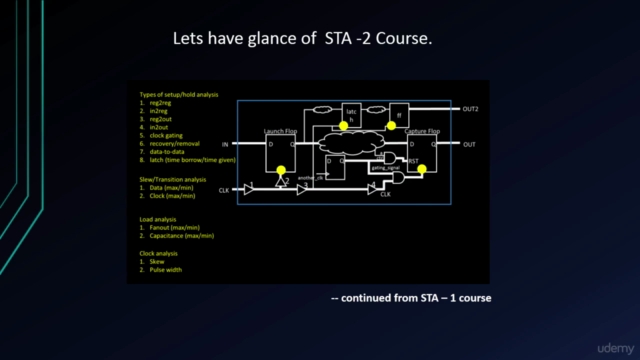

Welcome back, aspiring VLSI enthusiasts and engineers! In our previous course, "VSD - Static Timing Analysis - I," we took our first steps into the realm of timing analysis by learning about fundamental concepts like cppr, gba, pba, and more. Now, it's time to dive deeper with VSD - Static Timing Analysis - II, where we apply these concepts in real-world scenarios using the powerful opensource tool, 'Opentimer'.

🚀 What You Will Learn:

- Hands-On STA: Transition from theoretical understanding to practical application by analyzing actual chips.

- Real-World Challenges: Tackle complex designs like a USB controller or DDR memory using Opentimer.

- Interactive Learning: Engage with interactive exercises and homeworks that make the tool come alive under your hands.

💻 Why This Course?

- Free Access to Analysis Tools: Analyze your chip's performance at zero cost from the comfort of your home. It's like having a high-end lab right on your desktop!

- Industry-Relevant Skills: Gain expertise with tools used by professionals worldwide in the VLSI industry.

- Cutting-Edge Techniques: Learn about the latest advancements and features in STA, including PBA (Path Breakdown Analysis), CPPR (Critical Path Period Range), and block-based analysis.

🧠 Background & Development: Opentimer, an invaluable tool for VLSI engineers, was developed by the brilliant minds of Tsung-Wei Huang and Prof. Martin D. F. Wong at the University of Illinios at Urbana-Champaign (UIUC), IL, USA. It's a testament to open-source innovation and its role in shaping the future of VLSI design.

🔍 In-Depth Analysis with Opentimer:

- I will be utilizing Opentimer throughout this course to explain the advanced concepts from our previous STA course, ensuring a comprehensive understanding.

- We will also explore interface analysis and its significance in the VLSI domain.

🎉 Join Us on This Exciting Journey: I am thrilled to guide you through this enlightening journey where theory meets practice, and I hope you enjoy every bit of it as much as we do while creating these resources for you.

📅 Key Dates:

- Start Date: [Insert Date]

- Final Assignment Due: [Insert Date]

🤝 Your Instructor: Kunal Ghosh is an experienced VLSI engineer and educator with a passion for making complex concepts accessible and engaging. With a track record of successful courses and a deep understanding of STA tools, Kunal is here to support your learning journey every step of the way.

🎓 Ready to Elevate Your VLSI Skills? Enroll now and transform your understanding of chip timing analysis. Let's unlock the potential of your designs together! 🎓

Happy Learning, and see you in class! 😃

Course Gallery

Loading charts...