Randomization and IPC in SystemVerilog

Why take this course?

🎓 Course Title: Master Randomization & Inter-Process Communication (IPC) with SystemVerilog! 🚀

Headline: 🌟 Unleash the Power of Advanced Verification Techniques in Your Designs! 🌟

Introduction to SystemVerilog Verification 🔍

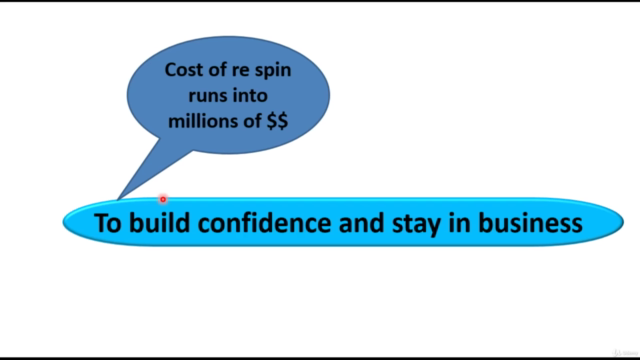

As the VLSI industry evolves, the demand for skilled verification engineers has skyrocketed. With an estimated 70% of professionals working in verification compared to design, mastering advanced verification techniques is more crucial than ever. The complexity and intricacy of today's designs necessitate a deep understanding of verification methodologies.

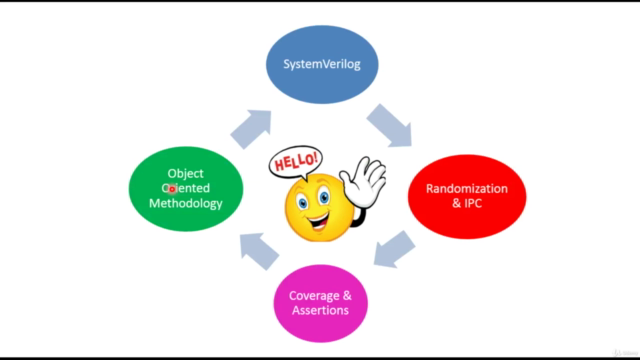

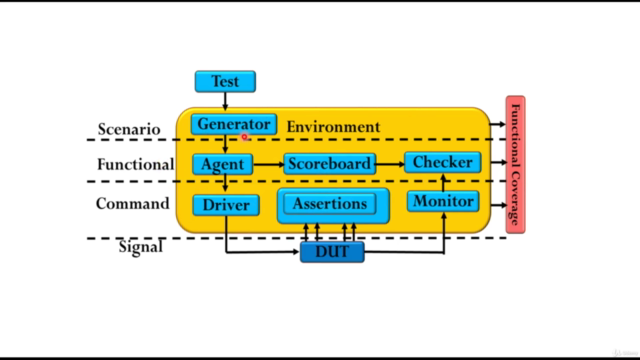

SystemVerilog, a powerful language for testbench development, offers a suite of constructs designed to streamline the verification process. However, harnessing its full potential requires a solid grasp of its features. This course is tailored for learners eager to delve into the world of Randomization and Inter-Process Communication (IPC) within SystemVerilog.

Course Highlights 🎯

-

Understanding the Basics: Ensure you have a firm foundation in SystemVerilog and object-oriented programming before diving into advanced topics.

-

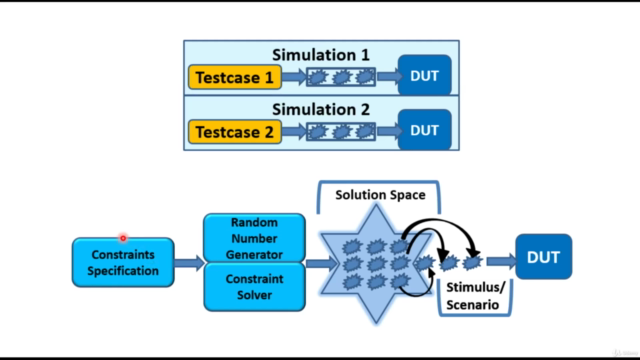

Randomization Mastery: Learn when, why, and how to apply constraint-randomization to your verification process, enhancing design coverage and effectiveness.

-

IPC Techniques Explored: Get hands-on with various IPC mechanisms such as events, semaphores, and mailboxes. Understand their applications and best practices for efficient communication between processes.

-

Real-World Examples: Engage with practical examples that demonstrate the application of randomization and IPC in real scenarios.

-

Self-Paced Learning: Progress through the course at your own pace, with regular quizzes to monitor your understanding and progress.

-

Simulation Practice: Put theory into practice by simulating course examples on EDA Playground and confirm your grasp of the concepts covered.

Course Outline 📚

-

Introduction to SystemVerilog Verification

- The role of verification in VLSI design

- Importance of advanced verification techniques

-

SystemVerilog Randomization Fundamentals

- Understanding randomization and its importance

- Constraint-randomization techniques

- Designing flexible and powerful testbenches with SystemVerilog

-

Inter-Process Communication (IPC) in SystemVerilog

- Overview of IPC mechanisms

- Detailed study of events, semaphores, and mailboxes

- Best practices for implementing IPC in your verification environment

-

Hands-On Practice

- Interactive exercises to solidify concepts learned

- Quizzes and self-assessments throughout the course

-

Simulation & Real-World Application

- Simulate examples using EDA Playground

- Apply learned techniques in practical scenarios

Why Enroll in This Course? ✨

-

Industry-Relevant Skills: Gain the skills that are in high demand by today's semiconductor industry.

-

Practical Learning: With a focus on hands-on exercises and real-world application, you'll be ready to tackle complex verification challenges.

-

Expert Instruction: Learn from an experienced instructor like Surendra Rathod, who brings years of expertise in SystemVerilog and advanced verification techniques.

-

Community of Learners: Join a community of peers who are also on the journey to mastering SystemVerilog verification.

Don't miss out on this opportunity to elevate your skills and become a verification expert with SystemVerilog! Enroll now and take the first step towards a successful career in VLSI design verification. 💫

Course Gallery

Loading charts...