FPGA Design with VIVADO HLS -High Level Synthesis

Why take this course?

🌟 Course Title: FPGA Design with VIVADO HLS - High Level Synthesis 🌟

Course Headline:

Design, Simulate, Synthesize & Export IP with VIVADO HLS: An FPGA Design Approach with C/C++ 🚀

Course Description:

As an added bonus, this course also guides you through the installation of Vitis HLS, setting up OpenCV in Vitis HLS, and performing examples using the Vitis Vision 2020.2 tool.

Embark on a comprehensive learning journey where you'll master FPGA design by leveraging the power of C/C++ programming. This course is tailored for beginners to advanced learners who wish to transition from basic High Level Synthesis (HLS) Design & C-Simulation to designing complex computer vision applications, such as Real Time Sobel Edge Detection.

🔹 Key Coverage:

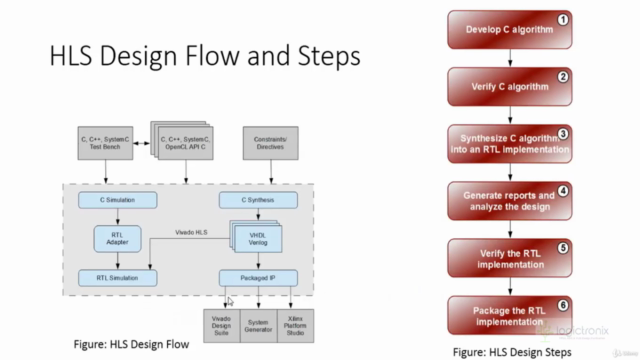

- Creating a new project on HLS

- Running C Simulation on HLS

- Synthesizing the HLS Project's to convert C/C++ source code into Verilog/VHDL and SystemC for efficient hardware implementation.

- Performing C/RTL Co-simulation to validate your designs at a higher abstraction level, saving time and resources.

- Exporting HLS Designs into an IP core format compatible with VIVADO IP Integrator.

- A dedicated session on designing Sobel Edge Detection IP in HLS, including its exportation to the VIVADO tool and implementation on a Zybo FPGA for real-world application.

By enrolling in this course, you will gain hands-on experience with:

- Designing complex systems using C/C++.

- Simulating your designs at a high level.

- Synthesizing your high-level designs into efficient hardware implementations.

- Implementing and exporting your HLS projects for practical applications.

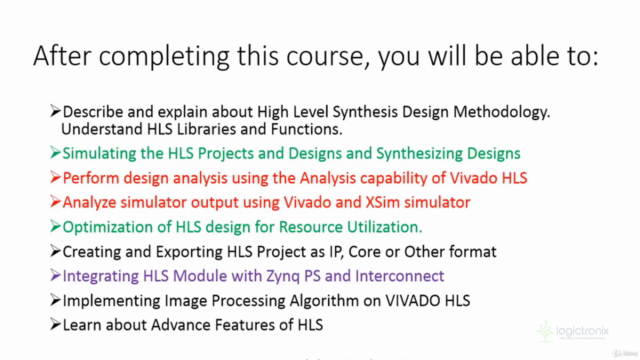

What to Expect: After completing this course, you will be fully equipped to design, simulate, synthesize, and implement or export HLS projects. You'll understand how to utilize the extensive C/C++ libraries provided by HLS for computer vision (like OpenCV), video/image processing, and complex mathematical computations. These are areas that are notoriously challenging when implemented directly in hardware description languages (HDL) or at the register-transfer level (RTL).

Lab Work:

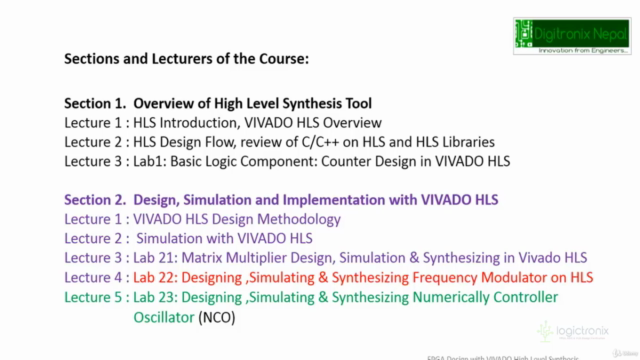

In this interactive lab, you will apply your newly acquired skills by designing, simulating, synthesizing, and implementing a variety of projects using C++. You will work on:

- Designing a Counter to understand basic counting operations.

- Simulating a Matrix Multiplier to handle matrix computations.

- Frequency Modulator design to generate signals with varying frequency characteristics.

- Numerically Controlled Oscillator (NCO Design) to create precise oscillations for digital signal processing tasks.

Additionally, you will integrate the exported HLS projects with the Zynq Processing System within VIVADO IP Integrator and proceed to synthesize and implement your designs on a Xilinx Zynq SoC using VIVADO IPI.

Join us for an enriching learning experience that combines theoretical knowledge with practical, real-world applications in FPGA design using VIVADO HLS! 🛠️💻✨

Course Gallery

Loading charts...