VERILOG / VHDL guided project tutorial UART design on FPGA

Why take this course?

🎓 Design of UART on FPGA using VHDL / Verilog Programming (Guided Project)

GroupLayoutin: Ezeuko Emmanuel

Course Title: Mastering FPGA UART Communication with VHDL / Verilog

🚀 Course Headline:

Design of UART on FPGA using VHDL / Verilog Programming (Guided Project)

🚀 Course Description:

Embark on a journey to master the art of UART (Universal Asynchronous Receiver/Transmitter) design on FPGAs through the powerful lens of VHDL/Verilog programming. This practical course is meticulously crafted to guide you step-by-step in creating your own UART project on an FPGA platform.

🔍 What You'll Learn:

-

Understanding UART Communication: Dive into the world of asynchronous serial communication, learning the nuances between full-duplex and half-duplex UART transmissions. Gain a deep understanding of their technical differences and practical applications.

-

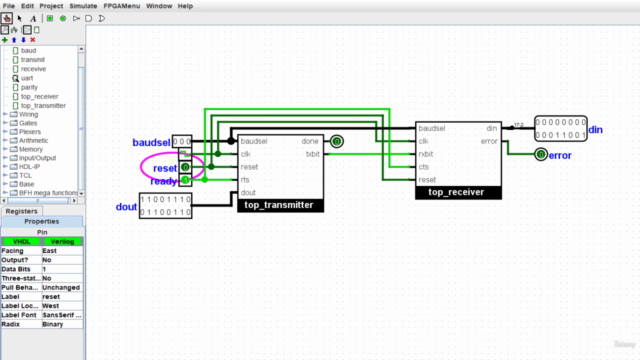

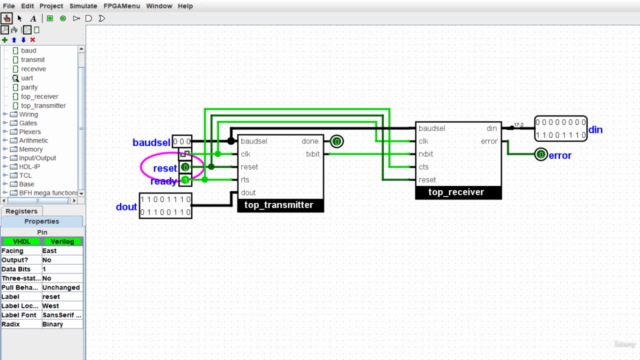

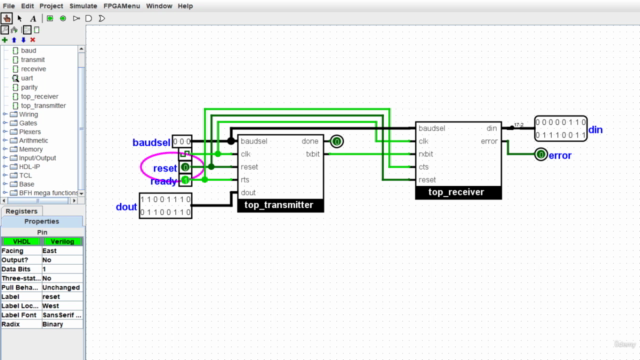

LOGISIM EDA Tool Mastery: Become proficient with LOGISIM EDA tool, which is essential for designing, testing, and simulating logic circuits. This tool will be your companion throughout the course as you bring your UART design to life.

-

Baud Clock Generation: Grasp the concept of a baud clock and its significance in UART communication. Discover how to synthesize a baud clock from the system clock and calculate the frequency for optimal operation.

-

Baud Rate Explained: Understand what a baud rate is, why it's crucial, and learn about standard baud rates. You'll also explore methods for generating these rates from your system clock.

-

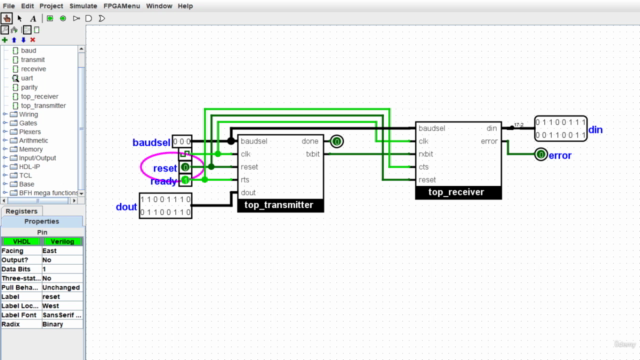

UART Transceiver Design: Learn how to design individual components like the receiver, transmitter, and their integration into a cohesive transceiver. Understand their roles, how they operate in tandem with the baud generator, and their connection to form a complete UART system.

📚 Course Structure:

This comprehensive course is segmented into three key modules, each focusing on a specific part of the UART design process:

- Receiver Design: Learn how to implement and configure the receiver module in your FPGA project.

- Baud Generator: Understand the principles behind generating a stable baud clock signal.

- Transmitter Design: Master the techniques to design and set up the transmitter module, ensuring effective data transmission.

📹 Guided Learning with Visual Aids:

This 17-video course is designed for optimal learning. With each module tackling a distinct part of the design, you'll find that the visuals, including arrows and pictures, make the tutorials easy to follow and understand. To enhance your learning experience, it is recommended to use the provided LOGISM circuit file while watching the tutorials.

🔍 Hands-On Learning Materials:

You will receive VHDL scripts and the LOGISIM circuit for lesson two, enabling you to apply what you've learned directly to your design process. No hardware is needed – just your PC and a willingness to learn.

Get Started Today!

With its concise and straightforward approach, this course will equip you with the skills necessary to confidently design and implement UART communication on FPGAs using VHDL or Verilog. 🎓👨💻📡

Enroll now and take your first step towards becoming an expert in FPGA UART design!

Course Gallery

Loading charts...